# PROCESSING AND RELIABILITY OF FLIP CHIP WITH LEAD-FREE SOLDERS ON HALOGEN-FREE MICROVIA SUBSTRATES

# Daniel F. Baldwin, Ph.D.

# **Grant Baynham**

Advanced Assembly Technology

Engent, Inc. – Enabling Next Generation Technologies

Norcross, GA 30071

Packaging Research Center Georgia Institute of Technology Atlanta, GA 30332

# Katarina Boustedt and Claes Wennerholm

Ericsson AB Kumla, Sweden

#### **Abstract**

Over the past several years, flip chip technology has been heavily focused on developing and refining the next generation of flip chip assembly processes and reliability; yet, little attention has been paid to the environmentally conscious aspects of manufacturing and high process throughput. With legislation pending on the use of lead in Europe and Japan and to limit environmental impact, flip chip technology must address new ways to meet safety and environmental requirements for the materials and processes used during assembly. The focus of this research is to characterize and implement environmentally conscious low cost flip chip material systems and processing, using two lead-free-solder interconnect systems and microvia halogen-free substrates, thus minimizing the environmental impact. The objective is to ensure that environmentally friendly materials are selected, along with acceptable process technology for all materials as well as for the flip chip assembly.

An assembly process for environmentally conscious low cost flip chip assembly to microvia laminate substrates will be presented, based on a fully integrated high speed flip chip assembly line. The process includes the flux application, chip placement, reflow process, and underfill processing. Flux and underfill material compatibility will be discussed, and data will be presented analyzing the quality of the solder joint formation and underfill adhesion to halogen-free solder masks. 204-µm pitch peripherally bump, daisy chain test chips with edge lengths of 5 mm and 10 mm respectively are used. Comprehensive reliability results are presented, comparing the two lead-free to tin/lead eutectic interconnect systems. The chips are assembled on microvia substrates with electroless nickel/immersion gold surface finish, comparing conventional to halogen-free FR-4

and solder masks. A fast flow snap cure underfill, qualified for use with eutectic tin/lead joints on conventional FR-4, is used for both board types.

Reliability results from air-to-air thermal shock testing are presented, comparing lead-free to eutectic interconnect systems mounted on conventional and halogenfree microvia substrates. Process and failure mode analysis are presented, based on x-ray inspection, C-SAM analysis, and assembly cross sections.

## Introduction

The trend in electronics of today is not only to smaller products, with more capability in less weight and power consumption, but also to greener, more environmentally friendly products. The consumer will in the near future want a product, which has a proven smaller impact on the environment, through ecological labeling and recycling considerations. The main driver in the lead-free movement is the customer demand, not legislation, especially not since the WEEE directive puts EU legislation back to 2008. In a 1996 survey 76% of consumers expressed a wish to change to environmentally friendly products, provided that price and quality were kept equal. In a 1999 follow-up, 50% of consumers had actually selected another product brand for environmental reasons [1].

At Ericsson the consumer request for lead-free and halogen-free electronic products is taken seriously. Targeted for the end of 2001, 80% of all new products will be both lead- and halogen-free. By the same timeline all new products will be completely free from beryllium oxide. The lead-free alloy of choice is SnAgCu, which is also clearly stated on the Ericsson internet site [2]. Furthermore, all Ericsson suppliers are required to have an environmental

management system, EMS, such as ISO 14000 or equivalent. This includes Design for Environment (DfE), material content declarations, compliance with Ericsson's Banned and Restricted substances lists, life cycle inventory data, end-of-life treatment, transportation of products, etc.

This is a study of the implementation of advanced lead-free solder interconnect technology and utilization of high-density microvia halogen free substrates defining a low-cost flip chip material and process technology leveraging state-of-the-art SMT infrastructure. This paper presents reliability and failure mode analysis of material systems based on air-to-air thermal cycle testing.

### **Background**

The 5th European Commission Directive on Waste Electrical and Electronic Equipment draft proposal was adopted 13 June. Some of the regulations that these documents comprise are the return of electrical and electronic equipment (EEE) to the producer free of charge, and the producers' responsibility for taking back and recycling products. This includes all EEE used by consumers, and also a wide range of professional uses, depollution and recycling for waste recovery by 60 - 80% by 2006 depending on product category. Furthermore, brominated flame retardants, PBB (polybrominated biphenyls) and PBDE (polybrominated diphenyl ethers), shall be substituted by 2008.

One implication that this directive has on the electronics industry is that the OEMs (Original Equipment Manufacturers) are responsible for take-back of products produced by their subcontractors, the EMS (Electronics Manufacturing Service) companies [3]. This may not have become fully clear before, and it brings a new way of thinking.

The Swedish Environmental Protection Agency gives a statement on its homepage [4]:

- IT products more than tripled 1992 1997 (by weight in tons)

- WEEE may contain mercury and PCB

- Brominated flame retardants, e.g. PBDE in focus

- PCB in breast milk decreasing, PBDE doubled in five years [5]

- Elevated PBDE levels in blood of electronic dismantling plant staff

- Producer responsibility for 10 product categories from 1 July 2001 in Sweden

Among the 10 product categories mentioned are telecom products, which certainly includes mobile phones. This means that although the WEEE directive relaxed the requirements for electronics manufacturer, for a Swedish mobile phone manufacturer such as Ericsson, the deadline for producer responsibility is in fact set for the third quarter of 2001.

## **Test Vehicles**

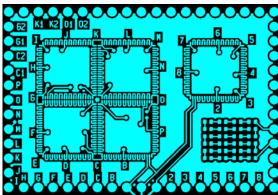

Two different sets of boards were used for testing: a standard FR-4 core and solder mask, and a halogen-free version of the same dielectric and solder mask, produced by the same board manufacturer in the same manufacturing The halogen-free materials used in the board manufacturing were from Hitachi, the laminate labeled MCL-RO-67 G, the prepreg MCL-RO-67 G, and the HDI dielectric MCF-4000G. The soldermask was Taiyo PSR 4000, halogen-free. The soldermask does generally not contain bromine, but the green pigment color uses phtalocyanine green chlorine. Therefore the soldermask is blue, which may cause alterations in vision and lighting systems for assembly. No such impact was seen in this project. Ericsson's halogen-free materials assessments claim that adhesion of soldermask to a halogen free substrate is adequate. The boards are 0.8 mm thick. The board trace metallization is copper with electroless nickel and immersion gold. The laminate has a T<sub>g</sub> of 150 C, as measured by TMA, and a V-0 flammability rating according to UL. The test vehicle used of flip chip assembly was panelized with eight individual boards, each having one 10 mm and 5 mm die site (Figure 1).

Figure 1. Test vehicle used for flip chip assembly.

### **Material Selection**

#### Lead-Free Alloy Selection

In selecting a lead-free solder for microelectronics applications, there are many considerations to be made. A drop-in replacement to eutectic SnPb is no longer expected to appear as the global "standard" alloy. However, consumer electronics companies outside Japan seem to have agreed on the SnAgCu systems, with the alloying elements ranging from 3.0 to 4.7 percent Ag and 0.5 to 3.0 percent Cu. The melting temperature of the various alloy compositions do not vary much, they are between 217 and 221 C.

For the experiments, a test die from Flip Chip Technologies (FCT) was used. It is the PB8 chip diced in two different sizes: a  $10 \text{ mm} \times 10 \text{ mm}$  with a dual array center cross of bumps and a  $5 \text{ mm} \times 5 \text{ mm}$ . The bump

height is nominally 95  $\mu$ m, the diameter 120  $\mu$ m, and the pitch is 204  $\mu$ m. The chips were bumped with Sn/Ag/Cu, an alloy marketed as LF2 by FCT. No solder was added in the chip attach process, neither as solder paste nor board plating, meaning that the solder in the chip bumps formed the entire joint. The solder alloy has a near eutectic at 217 - 218 °C. The recommended peak reflow temperature is 240 to 250 °C.

Reports indicate that SnAgCu alloys may need shorter time above liquidus to form proper solder joints, when compared to soldering profiles for SnPb. Indications are that with a peak temperature of only 10 C above liquidus, i.e., 227 C, solder joints of good reliability are formed [6].

#### Flux Selection

Fifteen fluxes of both dip and dispense types were tested to evaluate wetting, shear forces, and flux residues. Wetting studies using copper/nickel/gold test coupons and lead-free solder spheres were used as initial screening, followed by assembly tests with shear force measurements and cross-sectioning to achieve high quality solder joints. Among the parameters investigated were the flux amount: high vs. low, peak reflow temperature: high vs. low, and reflow atmosphere, air or nitrogen. The flux materials that gave the most consistent yield with lowest flux residues were selected for further testing. Test vehicles were assembled for X-ray and electrical continuity testing, die shear, and flux residue evaluation. It should be noted that incomplete solder joints were formed on some samples even though they passed electrical continuity testing.

#### Underfill Selection

The underfills were selected based on the Material Safety Data Sheets (MSDS), where any underfills containing acid anhydrides were rejected. The reason is that acid anhydrides are harmful to the respiratory system and requires a special permit for use in production in Sweden. The material flow times under the die were compared between underfill materials. In addition, the processing robustness of the underfills was considered, along with an adhesion and compatibility test performed with autoclave. The test vehicles were inspected using C-mode scanning acoustic microscopy (CSAM) to detect voiding in the underfill under the die, and cross-sectioned for further voiding analysis.

From the original five fluxes, two were selected for reliability testing with two underfills in nitrogen reflow and one flux / underfill system for reflow in air. This gave in total five flux/underfill combinations for test vehicle assembly: Underfills A and F with Fluxes B and C for nitrogen reflow and Underfill E with Flux B for reflow in air. Table 1 shows various properties of the underfills tested

in AATC. Vehicles were assembled, analyzed, and compared to standard eutectic lead-tin assemblies.

Table 1: Underfill Material Properties

|             | T <sub>g</sub><br>(°C) | CTE<br>( <t<sub>g)</t<sub> | CTE<br>(>T <sub>g</sub> ) | Modulus<br>@30°C |

|-------------|------------------------|----------------------------|---------------------------|------------------|

| Underfill A | 130                    | 35                         | 110                       | 4 GPa            |

|             |                        | ppm/°C                     | ppm/°C                    |                  |

| Underfill E | 139                    | 28                         | 85                        | 7 GPa            |

|             |                        | ppm/°C                     | ppm/°C                    |                  |

| Underfill F | 120                    | 31                         | 89                        | 4 GPa            |

|             |                        | ppm/°C                     | ppm/°C                    |                  |

# **Assembly Process**

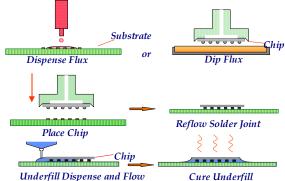

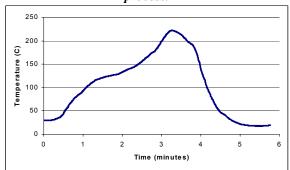

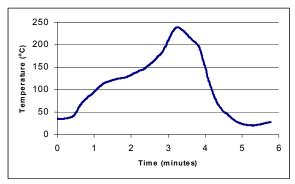

Figure 2 shows the basic process steps used for flip chip assembly. Assembly was performed with a Siemens F5, Asymtek flux jetter, and a BTU reflow oven. Underfill and fillets were dispensed using a Camalot 3700 and Asymtek M2000 dispense systems and cured in a batch convection oven. The reflow profiles for air and nitrogen reflow used for assembly are shown in Figures 3 and 4. The assembly process was analyzed based on CSAM analysis, X-ray, and cross-section microscopy.

Figure 2. The traditional flip chip assembly and underfill process.

Figure 3. Reflow profile used for assembly in air.

Figure 4. Reflow profile used for assembly in nitrogen

# **Test Setup**

Air to Air Thermal Cycling (AATC) was selected for long term reliability testing. The test conditions for AATC were -55 to 125°C, in 20-minute cycles with electrical continuity tests in situ and every 100 cycles. After every 200 cycles, samples were removed from the chamber for CSAM analysis. The desired reliability target was to have no failure occurring before 1000 cycles.

### **Test Results**

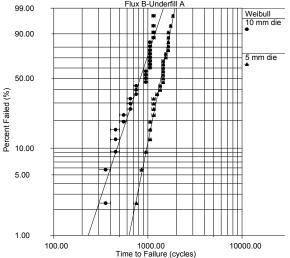

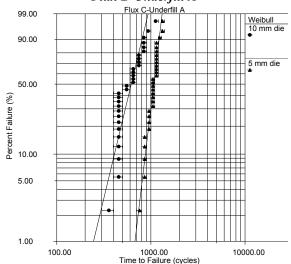

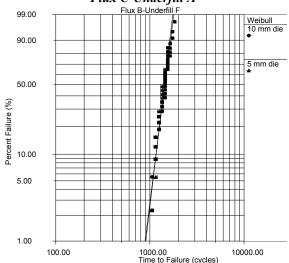

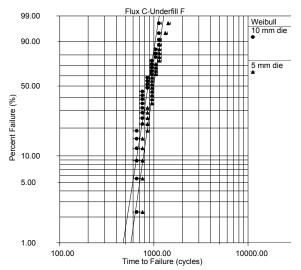

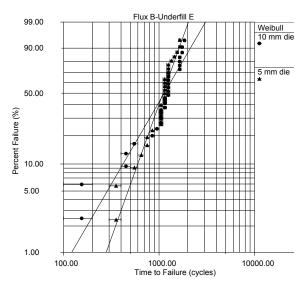

Results from thermal cycling varied among material sets. Only one material set passed the desired target of zero failures before 1000 cycles. Underfill F with Flux B performed the best having first failure at 1100 cycles for both die sizes. On average, the 5 mm die had a higher mean-time-to-failure (MTTF) than the 10 mm die. Weibull plots for the different material combinations are shown in Figures 5 through 9 Summary Weibull paramters ( $\beta$  and  $\eta$ ) for the AATC results for the different flux / underfill combinations are shown Table 2.

Table 2: Summary Results for AATC

|                      | Air to Air Thermal Cycling |       |          |       |  |

|----------------------|----------------------------|-------|----------|-------|--|

|                      | 10 mm die                  |       | 5 mm die |       |  |

|                      | MTTF                       | Slope | MTTF     | Slope |  |

|                      | (β)                        | (η)   | (β)      | (η)   |  |

| Underfill A – Flux B | 926                        | 3.33  | 1468     | 5.45  |  |

| Underfill A – Flux C | 670                        | 4.59  | 1116     | 9.22  |  |

| Underfill F – Flux B | 1506                       | 8.69  | 1483     | 9.30  |  |

| Underfill F – Flux C | 915                        | 6.92  | 1042     | 7.62  |  |

| Underfill E – Flux B | 1373                       | 1.90  | 1239     | 3.09  |  |

Figure 5. Weibull plot of failure data for Flux B-Underfill A

Figure 6. Weibull plot of failure data for Flux C-Underfill A

Figure 7. Weibull plot of failure data for Flux B-Underfill F

Figure 8. Weibull plot of failure data for Flux C-Underfill F

Figure 9. Weibull plot of failure data for Flux B-Underfill E

# **Failure Mode Analysis**

Failed test vehicles were inspected to determine the mode of failure. Methods used include C-mode Scanning Acoustic Microscopy (CSAM), Optical Microscopy, Scanning Electron Microscopy (SEM), and Energy Dispersive X-ray (EDX).

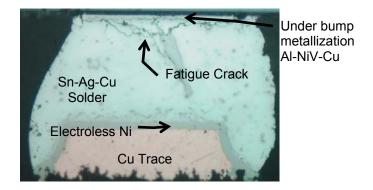

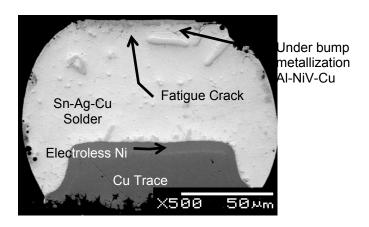

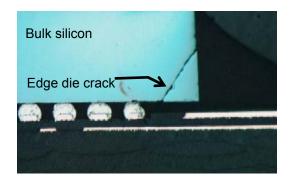

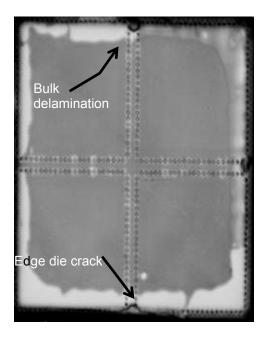

The dominating failure mechanism was found to be solder fatigue (Figures 10 & 11). Stresses generated from the difference in coefficients of thermal expansion (CTE) between chip and substrate were focused on singular solder joints where delamination of underfill occurred. This concentration of tension accelerated solder fatigue, which caused electrical failure. Two types of die cracking were

seen, edge die cracks were common when A was used, 12, and C-shaped cracks with Underfill F,

Figure 13.

Figure 10. Assembly cross-section displaying fatigue crack after 1000 cycles for Underfill A with Flux B.

Figure 11. SEM image displaying fatigue crack after 800 cycles for Underfill F with Flux C.

Figure 12. Assembly cross-section of edge die crack, Underfill A with Flux B.

Figure 13. CSAM for failed 10 mm die at 700 cycles Underfill F with Flux C.

### **Discussion**

The reliability of the flip chip devices is highly affected by the flux/underfill compatibility. Results showed that incompatibility of a flux/underfill combination resulted in loss of adhesion, which in turn accelerated cyclic fatigue due to CTE mismatch. Among underfills, the same underfill with different flux had different reliability and differing delamination. Samples reflowed in nitrogen atmosphere showed better overall reliability, which is evidenced by the higher Weibull slopes and MTTF. The flux/underfill combination reflowed in air had a fairly high MTTF but very flat slope.

The SnAgCu alloys are quite comparable to eutectic SnPb in their mechanical properties. Still, it is important to remember that also the use of eutectic SnPb for flip chip applications is considered less reliable than high lead alloys, such as 90Pb10Sn or 97Pb3Sn. However, the optismal SnAgCu composition of 95.4Sn3.1Ag1.5Cu provides a fine microstructure rendering high fatigue life, strength, and plasticity [7]. There may be a need for modifications to the under bump metallurgy to allow for even higher reliability with SnAgCu.

# Underfill Adhesion to Lead-Free Solder

The level of underfill adhesion to all surfaces in the flip chip system is what dictates the reliability in most flip chip systems. This includes the soldermask, exposed bare board, solder, chip passivation, and any flux residues that may be present. In the case of lead-free solders, there is a need to examine the difference in underfill adhesion as compared to the known good adhesion to SnPb alloy joints.

In a recent test performed at Ericsson in Kumla, 0805 chip components were attached to SnPb and SnAgCu solder surfaces using underfill. The underfill was cured to the specification given by the vendor datasheet. After curing the passive components were sheared off and the shear force per unit area was logged. There is a clear indication that the adhesion between underfill and the lead-free solder is better than that of underfill to eutectic tin lead.

The above results correlate to experiments conducted at Universal Instruments' consortium investigating lead-free flip chip. Delamination of underfill was significantly slower in the case of bumps of lead-free solder compared to eutectic SnPb [8]. The lead-free solder used in Universal's tests was Flip Chip Technologies' LF-1, which contains 85.9Sn3.1Ag10In1Cu, which is not the same alloy as the one used in the tests at Ericsson. This appears not to change the trend of better adhesion, though.

### **Conclusions**

A systematic procedure for evaluating flux and underfill materials for lead-free flip applications has been developed within the project. A robust process for flip chip with lead-free solders has been presented, although the lead-free processing window is extremely sensitive to such factors as flux amount, reflow atmosphere, and peak reflow temperature. Underfill adhesion tests indicate higher adhesion of underfill to lead-free solders than to SnPb. The study has demonstrated good reliability with a material set passing 1000 thermal cycles before first failure

### Acknowledgements

This paper is based on research carried out as a team effort at Georgia Tech, between Ericsson, Flip Chip Technologies, Siemens, and Georgia Tech. At Ericsson in Sweden, the work has been monitored and fitted into the rest of the research activities by Katarina Boustedt and Claes Wennerholm. Leena Korhonen performed the adhesion tests of underfill to lead-free solder. At Flip Chip Technologies, the team consists of Peter Elenius and Deborah Patterson, supporting the project with test die. Thanks are also extended to Georgia Tech's Center for Board Assembly and Packaging Research Center for use of their facility and for providing infrastructure support. Special thanks go out to Brian Lewis, Brian Smith and Paul Houston (Siemens) for their process expertise on conducting the experiments.

#### References

- [1] C. Jorgensen, "Working out the Lead-free June Bugs", Circuits Assembly magazine, Sept 2000

- [2] http://www.ericsson.com/environment

- [3] J. Linton, "The European Union's New Environmental Directives", Circuits Assembly magazine, Sept 2000

- [4] http://www.environ.se

- [5] C. de Wit, "Brominated Flame Retardants", Swedish EPA report 5065, 2000

- [6] R. G. Robertson, J. Smetana, "Fundamental Concerns in Lead-Free Implementation", Circuits Assembly magazine, Sept 2000

- [7] J. Hwang, "Lead-free Solder: the Sn/Ag/Cu System", SMT Magazine, July 2000.

- [8] S. Tonapi, K. Srihari, "Effect of No-Pb Bump Metallurgy on Flip Chip Underfill Delamination", Progress Report, Area Array Consortium, Universal Instruments, December 1999